If you square these bits in order to form a magnitude, you'll end up with 2B bits (for the real value squared) and 2B bits (for the imaginary value squared). But, assuming you don't have any overflows and you have the scaling right, then B bits come out of the FFT for each real and each imaginary component. That means that there'll be a scale factor within your FFT that you may need to know about. At full bit-width, you should have B+log_2(N)/2 bits coming out-but most implementations truncate this and scale a bit every other stage to keep it so that you have B bits going in and B bits coming out. If you have B real and B imaginary bits going into this FFT, then IIUC you should have B real and B imaginary bits coming out. If you did so on an N point FFT, than log_2(N) should be the number of bits in TUSER. You might find the article and associated code valuable.Īren't we supposed to check Index of the FFT peak on TUSER? I recently wrote about debugging AXI streams, such as the FFT would either produce or consume. Here's an approximate log-magnitude block I built some time ago. Here are some other things you might be interested in though. Why would TUSER have any useful information in it at all?

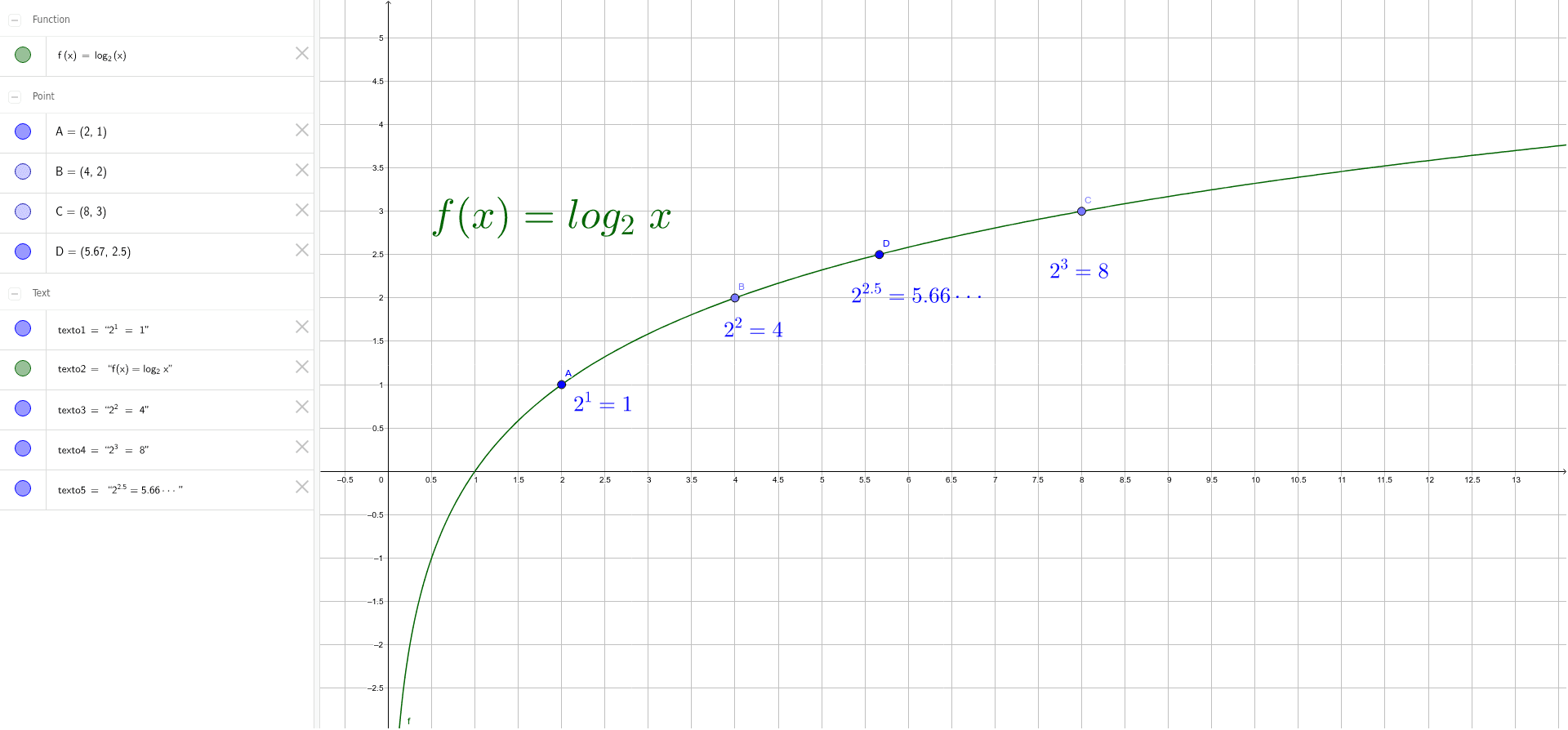

I'm not sure I follow your third question. However, if you wanted to separate out the bits from an FFT output, I'd be surprised if you didn't have to specify which bits of the slice you were actually interested in. I don't normally use Xilinx's slice primitive. With only 8-bits, you don't have a lot to work with. Be careful of overflow in this calculation. For complex exponentials of equivalent magnitudes, the magnitudes at the output of the FFT *should* be the same. Your kind Response will be highly know the effect on the FFT magnitude of using just a sine vs a sine plus a cosine, try mapping the inputs to complex exponentials first. Input Data Width:8, Phase Factor Width: 8 Implementation: Fixed Point, Block Floating Point, Covergent Rounding Transform Size: 4096, Target Clock:100M, Radix2 Busrt I/O Architecture As Log base 2 (4096) is 12.Įxpected Index: 50K/ (100M/4096) = 2.048 : 10Ĭonfiguration: Phase Generator and SIN COS LUT, System Clock : 100Mįixed, Phase Offset: None, Output Selection: Sine and Cosine Third thing is that, if we select SINE and COSINE option in DDS, then in FFT Magnitude block, how many bits for Tuser index will represent Sine and Cosine Magnitude. Secondly, I am not sure whether my FFT Magnitude Block is right or not (Figure Attached), I have used two Slices at the output of FFT IP m_axis_data_tdata to separate Real and Imaginary parts, but do we need to specify separte MSBS and LSBS in it or not. I am trying to generate Sinusoidal frequency using DDS Compiler in Vivado Block Designing and want to check its FFT Magnitude.įirst thing is that what will be the effect on output magnitude and xk_tuser index of FFT, if we use simple SINE or SINE AND COSINE.Īs in general we get two peaks for sine wave while for SINE AND COSINE we get single peak with added magnitude (please correct me if I am wrong).

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed